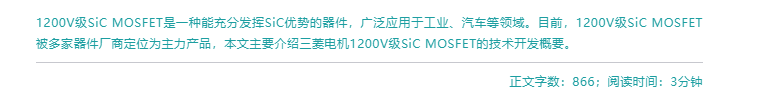

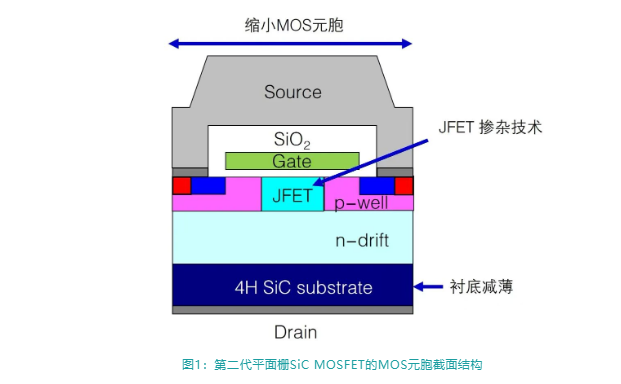

截至2024年,三菱電機已量產第二代平面柵SiC MOSFET芯片,并配套于各種模塊實現產品化。圖1顯示了第二代平面柵SiC MOSFET的MOS元胞截面結構及其特點。首先,使用n型離子注入技術(JFET摻雜)來優化MOS元胞JFET區的結構,降低了JFET區域的電阻。此外,與以往相比,縮小了MOS元胞的尺寸,通過提高MOS溝道密度來降低電阻,并通過使SiC襯底更薄來降低電阻。通過這些改進,如圖2所示,三菱電機的第二代SiC MOSFET與第一代相比,導通電阻降低了30%以上。此外,用于保持第二代SiC MOSFET耐壓的終端結構采用了FLR(Field Limiting Ring),形成適當的表面保護膜。

共0條 [查看全部] 網友評論