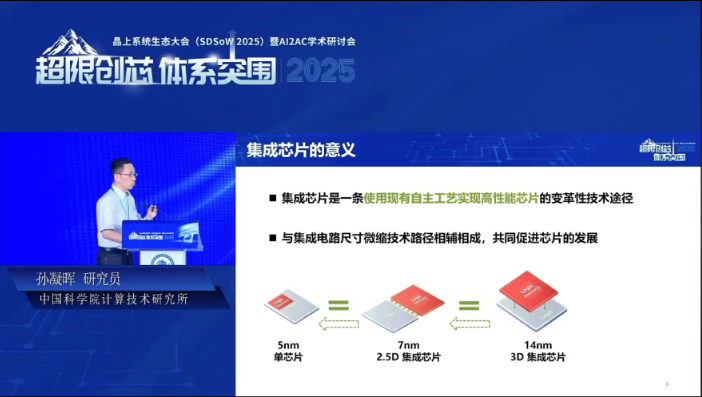

隨著摩爾定律的發(fā)展逐漸放緩,集成芯片與芯粒(Chiplet)技術對高性能芯片的設計與制造愈加重要。近日,中國工程院院士、中國科學院計算技術研究所研究員孫凝暉在2025年度晶上系統(tǒng)生態(tài)大會(SDSoW)上指出,集成芯片是一條使用現(xiàn)有自主工藝實現(xiàn)高性能芯片的變革性技術途徑,而芯粒集成度(數(shù)量和種類)的大幅提升帶來了三大科學問題。

孫凝暉表示,集成芯片是提升芯片性能的新路徑。傳統(tǒng)芯片是晶體管在二維平面上集成制造的芯片;相比之下,集成芯片先將晶體管集成具有特定功能的芯粒,再將預制好的芯粒按照需求三維集成為芯片。集成芯片的優(yōu)勢是通過兩次集成大幅提高晶體管總量,集成規(guī)模最大可到整片晶圓;芯粒的模塊化可降低芯片設計與生產(chǎn)成本。

“集成芯片是一條使用現(xiàn)有自主工藝實現(xiàn)高性能芯片的變革性技術途徑。它與集成電路尺寸微縮技術路徑相輔相成,共同促進芯片的發(fā)展。”孫凝暉說道。從產(chǎn)業(yè)實踐來看,在先進集成技術賦能下,采用14nm工藝可實現(xiàn)7nm甚至5nm工藝的芯片性能。

從設計范式來看,現(xiàn)有芯片設計范式是從晶體管到芯片,自下而上地堆疊,這樣的范式伴隨著兩個原生問題:一是晶體管數(shù)量巨大,使得設計復雜度不斷增高,二是產(chǎn)業(yè)易被掌握先進工藝的制造廠商主導。

而集成芯片引入了系統(tǒng)工程學的理念,從應用需求出發(fā),在堆疊法的基礎上,引入了自上而下的構造法:一是最優(yōu)化多芯粒功能分解,二是大規(guī)模芯粒高效組合,三是芯粒3D高密度集成。

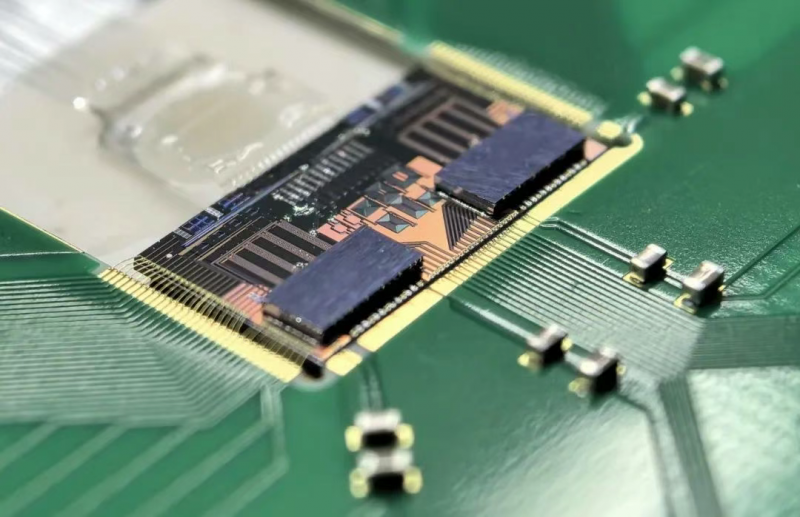

基于硅光芯片的3D芯粒集成方案

孫凝暉指出,芯粒集成度的大幅提升帶來了新的科學問題,主要體現(xiàn)在以下三方面。

一是芯粒的數(shù)學描述和組合優(yōu)化理論。

如何將復雜的功能需求,分解并映射到大規(guī)模的芯粒構件上?

孫凝暉指出,少量芯粒集成時,映射關系簡潔;而將復雜功能分解到大量芯粒時,需要借助數(shù)學運算。另外,傳統(tǒng)集成電路針對微觀晶體管的數(shù)學描述不適用于芯粒尺度,亟需建立新的數(shù)學理論。

針對集成芯片“分解”問題的研究思路,他認為,與傳統(tǒng)芯片中采用布爾代數(shù)表示晶體管功能不同,可以采用函數(shù)理論對多芯粒系統(tǒng)進行抽象描述,并基于復雜函數(shù)的分解優(yōu)化,建立對集成芯片的芯粒最優(yōu)分解的建模和分析。

為此,需要重點關注集成芯片的抽象數(shù)學描述,設計復雜空間建模、降階與優(yōu)化理論,以及跨層次、隨機、不可精確計算函數(shù)的優(yōu)化。

二是大規(guī)模芯粒并行架構和設計自動化。

隨著芯粒的數(shù)量和種類大幅提升,怎樣應對芯片設計復雜度的爆炸式增長?

孫凝暉指出,目前集成芯片的芯粒種類少、數(shù)量少,可調整的設計參數(shù)有限,并行設計的難度較低。但是到了大規(guī)模芯粒集成時,就要考慮分解效率、三維自動化布局布線等新問題,需要新的EDA算法。而現(xiàn)有EDA工具用于以晶體管為單元的平面電路設計,需要以芯粒為單元的三維EDA工具。

針對集成芯片“組合”問題的研究思路,他認為,現(xiàn)有EDA工具主要基于模型/暴力搜索等方法實現(xiàn)自動化。針對集成芯片,可以引入專家知識+人工智能協(xié)同的新方法,構建多芯架構和集成芯片設計的EDA工具。

為此,需要重點關注的方向包括:多芯并行體系結構和互聯(lián)接口,集成芯片的綜合、布局布線算法,以及多芯并行的編譯原理與軟件棧。

三是芯粒尺度的多物理場耦合機制與界面理論。

不同功能和種類的芯粒在形成界面時,如何優(yōu)化電、熱傳導,避免應力破壞?

孫凝暉表示,少量芯粒集成時僅需在二維層面分析電、熱、力傳導,距離遠耦合度低,效應易預測。而大規(guī)模芯粒集成時,擴展到三維空間,多層堆疊結構帶來了復雜界面的物理量傳導耦合問題。此外,傳統(tǒng)集成電路對微觀晶體管電熱力傳導建立的物理模型,不適用于芯粒尺度的預測分析。

針對集成芯片“集成”問題的研究思路,他認為,與傳統(tǒng)芯片中微觀(晶體管)和宏觀(芯片)層面分立的電—熱—力的多場耦合效應不同,需以芯粒作為連接微觀與宏觀的核心樞紐,以微觀物理理論為基礎去構建芯粒尺度的多物理場,以及多界面耦合的快速、精確的仿真計算方法。需要重點關注的方向包括電—熱—應力交互的多物理場仿真,大功率集成芯片的電源管理與散熱理論,以及3D互連界面的可靠性。

共0條 [查看全部] 網(wǎng)友評論