英特爾今天在美國舉行的 IEDM 會議上展示了使用背面電源觸點將晶體管縮小到 1 納米及以上的關鍵技術。

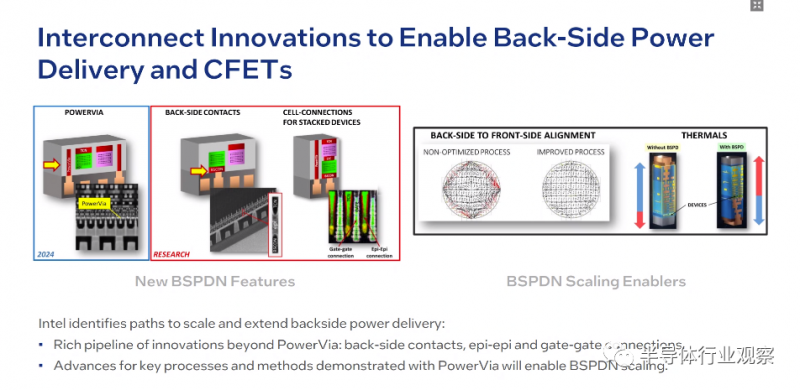

Intle已經展示了背面電源通孔,從晶圓背面連接電源軌,這將在Intel 18A 1.8nm工藝技術中實現。背面電源觸點將能夠縮小至 1 納米及以上。

“我們非常高興成為第一個在intel 18A 工藝中實現背面電源通孔的公司,”Components Research 芯片中尺度工藝開發總監 Paul Fisher 說道。

這是堆疊帶狀晶體管下一步的關鍵部分。

“在 IEDM 上,我們將提供電源通孔之外的全面描述,”Intel 院士兼技術開發總監 Mauro Kobrinsky 說道。

“在背面供電處理器之前,內置有多層金屬線。摩爾定律驅動更多的晶體管,這驅動更多的層和更小的電線,從而增加了復雜性和成本。每一層都必須提供信號和電源線路,這通常會導致優化妥協和資源競爭、互連瓶頸,這變得越來越具有挑戰性。”

“背面電源從根本上改變了這種情況,通過設備兩側的互連和垂直互連,通過適當的電源。我們明年能夠在intel 20A 和intel 18A 中部署這項技術,這意味著正面的電線更少,這樣我們就可以放寬間距,不再需要做出優化妥協,”他說。

“通過我們的研究,除了電源之外,還涉及背面接觸,這使我們首次能夠從設備的兩側連接晶體管。我們已經能夠在我們的研究車輛中制造這些觸點,并且正面和背面觸點相匹配,而無需使用電源過孔進行布線。這使我們能夠降低電池的電容,從而以更低的功耗獲得更高的性能,”他說。

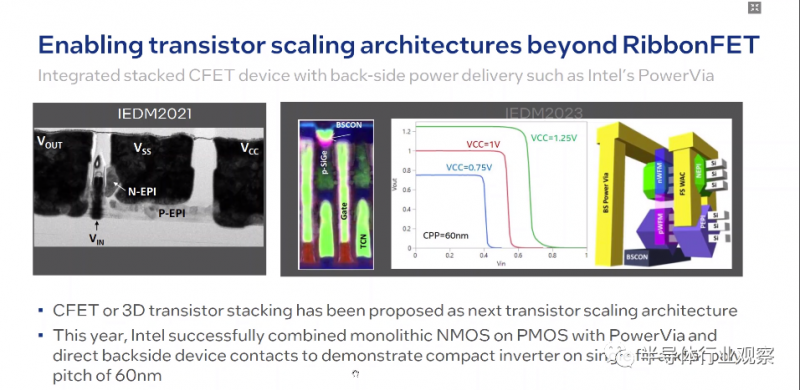

英特爾已使用這種互連技術將晶體管與 NMOS 器件堆疊在帶狀 PMOS 之上,以構建反相器門。

“這對電源和信號同時產生了一個有趣的挑戰,包括背面接觸和電源過孔。有意義的堆疊過程不僅需要能夠堆疊設備,而且還需要以節省空間的方式互連它們。如果互連增加了占位面積,我們就會失去我們試圖實現的晶體管密度的影響,因此必須具有低占位面積、背面接觸和電源通孔,而堆疊柵極連接是實現這一點的關鍵,”他說。

堆疊中的下部晶體管連接到晶圓的背面,頂部晶體管連接到頂部,同時通過堆疊連接。這避免了在堆棧頂部需要更多觸點。關鍵的一步是,英特爾確認使用背面接觸不會影響熱行為,因此隨著時間的推移,標準的熱改進會隨著時間的推移而擴展。

“這使我們第一次能夠對齊晶圓正面和背面的特征,并且我們已經確定了正面到背面對齊的多個路徑。我們在實現這種疊加方面做出了重大改進。這對于實際的設備堆疊實施至關重要,”他說。

堆疊式 CFET 互補器件采用可擴展的工藝構建。

英特爾首席工程師 Marko Radosavljevic 表示:“我們的晶體管縮放和互連工作之間存在巨大的協同作用,因為我們希望最大限度地提高密度。”

“如果沒有背面接觸,我們將需要額外的頂部接觸,這會增加占地面積。我們在規模更大的研究車輛上將背面接觸與器件堆疊結合起來,其多晶硅節距為 60 納米,與我們在 2021 年展示的工作相比,其規模相當大。”他說。

英特爾已將堆疊晶體管用于單個鰭上的逆變器門

“我們有三個帶,nmos 和 pmos 各三個,我們必須弄清楚如何創建 pn 結,”Radosavljevic 說。“這是一項新穎的技術,我們需要擴展到垂直圖案化技術,以便在堆棧的頂部或底部進行操作,并且我們需要單獨的連接。我們使用電源通孔將頂部器件連接到晶圓背面,并使用背面電源觸點連接底部器件。我們使用門控制器將門連接在一起。”

“inverter 需要連接晶體管的源極,我們使用頂部的環繞式接觸,以一種節省空間的方式將頂部器件連接到底部器件,而不是繞過器件,我們將在硅上面。”

“inverter 是我們可以創建的最簡單的電路,它是在同一個晶體管中創建的,具有器件堆疊以及電源通孔和背面接觸。我們對這項研究的前景感到非常興奮,因為這是未來設備密度的顯著提高,”他說。

共0條 [查看全部] 網友評論