一種新型1.2kV SiC MOSFET器件的精確SPICE模型的開發(fā)

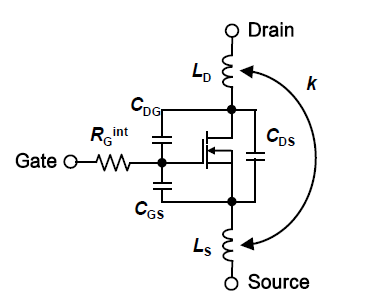

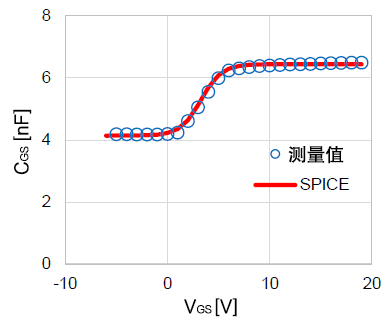

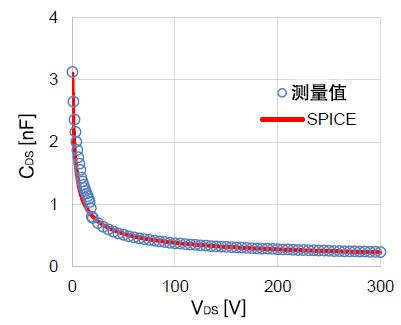

TakashiMasuhara1, Takeshi Horiguchi1, Yasushige Mukunoki1,Tomohide Terashima2, Naochika Hanano2, and Eisuke Suekawa2本文介紹了一種新型1.2kV SiC MOSFET分立器件的SPICE模型。所開發(fā)的SPICE模型擬合了非線性寄生電容,并且具有飽和區(qū)的精確輸出特性;同時該模型可以準確復現(xiàn)柵極驅(qū)動回路和主功率回路的開關(guān)波形,凸顯出該模型作為一種設(shè)計工具在未來具有巨大的應(yīng)用潛力。SPICE模型在電路仿真中已被廣泛用作標準模型。一些器件制造商已經(jīng)提供了他們的SiC器件SPICE模型,這使得電路設(shè)計工程師能夠評估功率變換器電路中的SiC器件開關(guān)性能。近來,SPICE模型一直是一個熱門的研究課題,不斷提高其準確性和實用性[1]。例如,科銳公司為他們的1.2kV分立SiC MOSFET引入了第3代SPICE模型,來更好地復現(xiàn)輸出特性和溫度依賴性[2]。SPICE模型的準確性是一個非常關(guān)鍵的問題,也是有待進一步研究的課題。文章介紹了一種新型1.2kV/30A SiC MOSFET分立器件的SPICE模型。此SPICE模型擬合了非線性寄生電容:依賴于VGS的CGS,依賴于VDS的CDS,依賴于VGS和VDS的CDG[3-5];同時它還包含內(nèi)部柵極電阻、具有耦合系數(shù)的寄生電感和精確的飽和區(qū)輸出特性。通過將SPICE仿真結(jié)果與雙脈沖測試(電感負載)所測得的開關(guān)波形進行比較來驗證SPICE模型的準確性。以三菱電機新開發(fā)的1.2kV/30A SiC MOSFET分立器件作為被測器件DUT(Device Under Test)。圖1給出了SPICE模型的等效電路圖,包含內(nèi)部柵極電阻(RGint)、源極寄生電感 (LS)、漏極寄生電感(LD),兩者之間的耦合系數(shù)(k)、三個寄生電容(CGS、CDS和CDG)和表征輸出特性的通用MOSFET內(nèi)核。內(nèi)部柵極電阻RGint作為CGS的等效串聯(lián)電阻,由LCR測試儀在頻率1MHz 下測試得到,此處設(shè)置為2.7Ω。通過諧振原理測試得到TO-247封裝的寄生電感,LS為5.0nH,LD為2.4nH,兩者之間的耦合系數(shù)為-0.69[3]。圖2顯示了CGS、CDS和CDG三個寄生電容測量值和SPICE模塊近似值的比較。圖2(a)將CGS繪制成VGS的函數(shù),其中藍色圓圈表示測量值,紅色實線表示SPICE代碼中描述的近似值。CGS是通過對被測器件施加VGS,用LCR測試儀測量的,并用雙曲正切函數(shù)來擬合。由于柵氧層下面的寄生電容,在VGS為正且直到7V時,CGS是不斷增加的。另一方面,負VGS區(qū)域的電容保持在4nF恒定值。此種情況不同于其他制造商的SiCMOSFET,這在我們之前的研究中說明過[5]。圖2(b)將CDS繪制成VDS的函數(shù)。CDS是由圖示儀通過對被測器件施加正VDS和恒定VGS=0V測量得到。CDS對VGS的依賴性是可以忽略的,這里不做考慮。CDS用VDS的簡單冪函數(shù)來近似。圖2(c)將CDG繪制為VGS和VDS的函數(shù)。如文獻2中所描述的,CDG是在米勒平臺時柵極電流波形分析得到。為了更好地評估CDG,需要減去在米勒平臺時流入CGS的微小電流。CGD近似為VGS的雙曲正切函數(shù)和VDS的冪函數(shù)的組合。

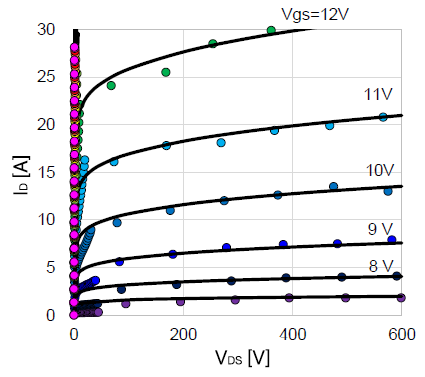

圖3給出了測量和仿真輸出特性的比較,其中圓點代表測量值,實線代表仿真值。利用圖示儀對線性區(qū)域(圖3(a))的輸出特性進行評估,利用文獻6中報道的方法對開通波形進行分析得到高達600 V的飽和區(qū)域(圖3(b))輸出特性。在線性區(qū)域(VDS≤VDS(sat)),采用基于α冪律分布的MOSFET模型函數(shù)[7]。在此基礎(chǔ)上,對較高的VGS區(qū)域進行精確的匹配,使其通態(tài)電阻準確。在飽和區(qū)(VDS>VDS(sat))中,定義了VDS的冪函數(shù),該函數(shù)可復現(xiàn)600V以下的輸出特性。

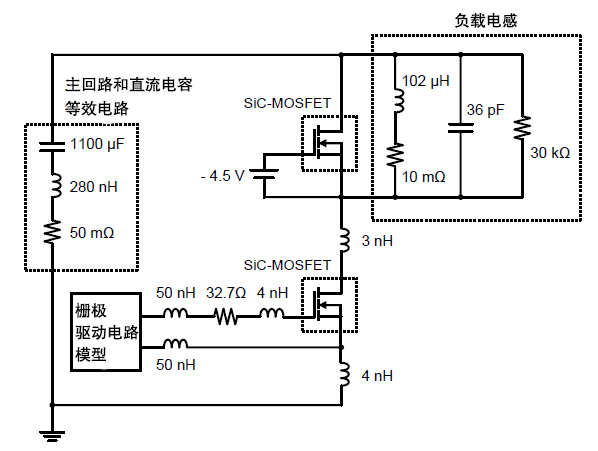

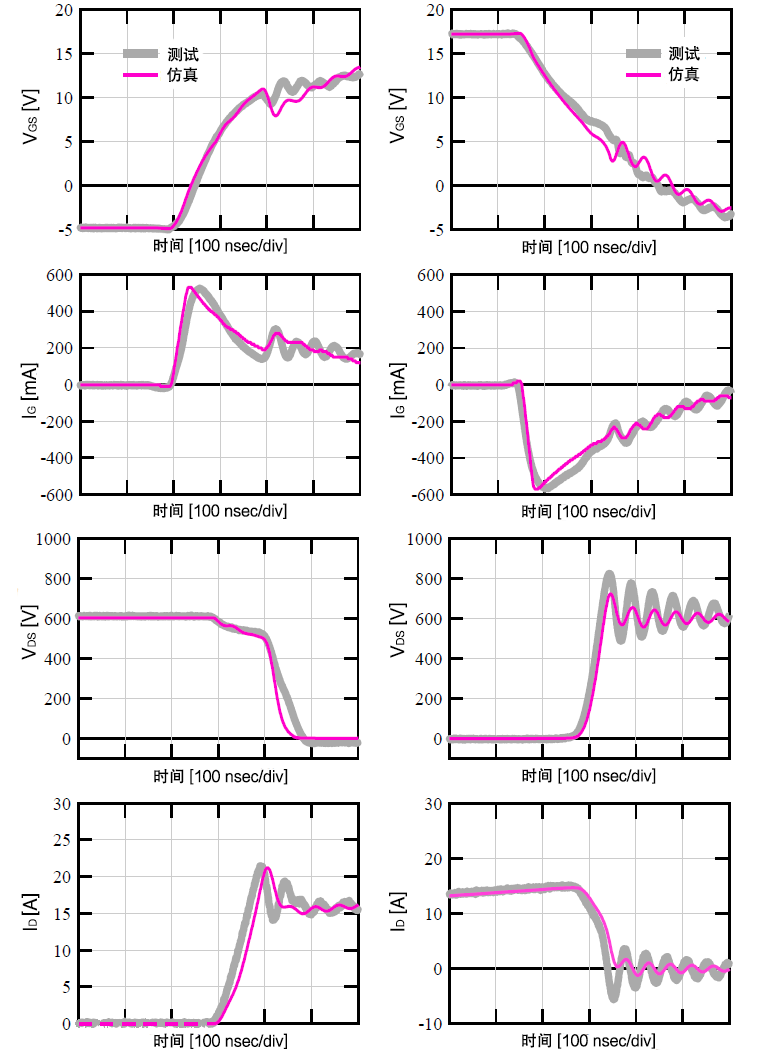

該模型的開關(guān)波形由電感負載雙脈沖開關(guān)試驗來驗證。在直流電壓為600V、漏極電流為15A的情況下,通過開關(guān)測試來驗證。圖4為雙脈沖開關(guān)測試的電路原理圖。該拓撲是一個半橋電路,其中負載電感與上橋臂SiC MOSFET并聯(lián)。下橋臂SiC MOSFET作為被測器件,上橋臂SiC MOSFET作為續(xù)流二極管,其柵極偏壓為-4.5 V。圖4中用帶虛線方框來標注直流電容和主功率回路組成的等效電路模型。電路圖中還包含下橋臂SiCMOSFET每個輸出端子的連接線引起的寄生電感。下橋臂SiC MOSFET的外部驅(qū)動電阻為32.7Ω。對柵極驅(qū)動電路也進行了建模[6]。柵極電路的輸出與下橋臂SiC MOSFET之間的外部驅(qū)動電阻通過兩條雜散電感為50nH的導線所組成的雙絞線進行連接。圖5顯示了測試和仿真開關(guān)波形的對比。總的來說,SPICE仿真波形與測試結(jié)果顯示出良好的一致性。在圖5(b)的關(guān)斷波形中,僅在測試中觀察到VDS的明顯電壓波動。造成這種偏差的原因是缺乏實際主功率回路中與頻率相關(guān)阻抗的精確模型。這超出了本文的范圍,有待作為一個未來的研究方向。圖5:直流電壓600V、漏極電流15A試驗和仿真開關(guān)波形對比本文提出了一種新開發(fā)的1.2kV/30A SiC MOSFET器件SPICE模型。所建立的SPICE模型具有非線性寄生電容和高達600V的精確輸出特性,與測試結(jié)果吻合良好。該模型有望在SiC MOSFET柵極驅(qū)動電路和主電路設(shè)計中廣泛應(yīng)用。

共0條 [查看全部] 網(wǎng)友評論